This page contains information about the current ongoing group project as well as some older ones

Approximate Computing

Ongoing

Many classes of applications exhibit significant tolerance to inaccuracies in their computations. Some examples include image processing, multimedia applications and machine learning. These inaccuracies can be exploited to build circuits with smaller area, lower power and higher performance. One of the main problems with approximate computing is that it is highly data dependent. The resultant micro-architecture will depend on how aggressively it is approximate based on the training data. Often random inputs are used. The error can nevertheless reach intolerable levels in the case that the final workload significantly differs from the training data used during the approximation.

The main problem is that most of the previous work on approximate computing focuses on a particular VLSI design level. Although, leading to promising results, only a subset of all possible optimizations are visible at each level. E.g. some work in the past has dealt with approximate computing at the behavioral level, focusing mainly on the limitation of the precision or data type simplification of variables. Moreover, previous work assumes a single input data distribution (IDD) when approximating the design, often random data is used. In reality the final workload can differ significantly from the IDD used when approximating the design. It has also been shown, that workloads tend to change over time, hence, this canlead to intolerable error levels.

Key References:

S. Xu and B. Carrion Schafer, Towards Self-Tunable Approximate Computing IEEE Transactions on Very Large Scale Integration (TVLSI) Systems, pp.778-789, Vol.27(4), 2019.

B. Carrion Schafer,”Approximate Computing: Mitigating the Risk of Dynamic Workloads“, IEEE COMSOC Technology News (CTN), 2017 [html].

S. Xu, B. Carrion Schafer,”Exposing Approximate Computing Optimizations at Different Levels: From Behavioral to Gate-Level“, IEEE Transactions on Very Large Scale Integration (TVLSI) Systems, Vol. 25, Issue 11, pp.3077-3088, 2017.

S. Xu and B. Carrion Schafer, Approximate Reconfigurable Hardware Accelerator: Adapting the Micro-architecture to Dynamic Workloads, International Conference on Computer Design (ICCD), pp. 1-7, 2017.

B. Carrion Schafer,Enabling High-Level Synthesis Resource Sharing Design Space Exploration in FPGAs through Automatic Internal Bitwidth Adjustments, IEEE Transactions of Computer Aided Design (TCAD), Volume 36, Issue 1, pp. 97-105, Jan. 2017.

Behavioral IP Protection

Ongoing

Semiconductor companies were in the past vertically integrated. Companies like IBM, Intel and Samsung, still follow this strategy. However in the past 20 years the fastest growing semiconductor companies were fabless companies. These design companies focus on the architectural development of the HW and contract silicon foundries for the manufacturing process. Some examples include Altera, Broadcom, Cisco, Qualcomm and Xilinx. Due to the cost of setting up their own manufacturing facilities, this trend is predicted to grow. Even some traditionally vertically integrated companies, have divested their manufacturing facilities (or part of them) e.g. AMD, Fujitsu, Renesas.

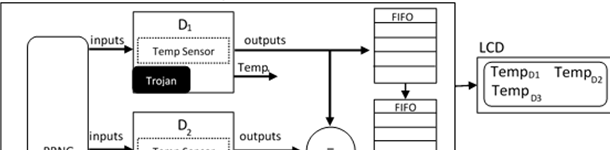

Although from the economical point of view, the horizontal integrated model is sound, it poses many new challenges. This business model leads to these companies not having control over the manufacturing process and hence do not control e.g. how many ICs the foundry has actually manufactured and if the design has been maliciously modifed to include e.g. HW Trojan. On the other hand ITRS suggest that by 2020 a 10x productivity increase for designing complex SoCs is needed. The main factor predicted to help achieving this goal is the use of IPs (third party or re-use of previously used components). ITRS estimates that at around 90% of the SoCs will be composed of IP components. Having relinquished so much control for economic reasons opens the debate to how trustworthy the HW systems actually are. This is especially the case for mission-critical applications, because these applications should be extremely secure, but typically only about one to two percent of the global ICs target these applications. Although a fraction of the total IC market, they are essential to national security, but is economically infeasible to have a separate supply chain for them. In this project we address the issue of HW trustworthiness from the behavioral-level intellectual property protection (IPP)point of view.

Key References:

C.G. Sathe, Y. Makris and B. Carrion Schafer, Efficient and Secure Cloud-based Split Logic Synthesis, Asia and South Pacific Design Automation Conference (ASP-DAC), pp.1-6, 2025.

J. Chen and B. Carrion Schafer, Thermal Fingerprinting of FPGA Designs through High-Level Synthesis, ACM Great Lakes Symposium on VLSI (GLSVLSI), pp. 1-4, 2019.

C.G. Sathe, Y. Makris and B. Carrion Schafer, MANTIS: Machine Learning-Based Approximate ModeliNg of RedacTed Integrated CircuitS, Design, Automation, and Test in Europe (DATE), pp. 1-6, 2023.

B. Hu, J. Tian, M. Shihab, G. R. Reddy, W. Swartz Jr., Y. Makris, B. Carrion Schafer, C. Sechen, Functional Obfuscation of Hardware Accelerators through Selective Partial Design Extraction onto an Embedded FPGA, ACM Great Lakes Symposium on VLSI (GLSVLSI), pp. 1-6, 2019.

N. Veeranna and B. Carrion Schafer, Efficient Behavioral Intellectual Property Source Code Obfuscation for High-Level Synthesis, 18th IEEE Latin American Test Symposium, Bogota, Colombia, 2017.

N. Veeranna and B. Carrion Schafer,”Trust Filter: Runtime Hardware Trojan Detection in Behavioral MPSoCs“, Journal of Hardware and Systems Security, Springer, 2017.

N. Veeranna and B. Carrion Schafer,”Hardware Trojan detection in Behavioral Intellectual Properties(IPs) using Property Checking Techniques“, IEEE Transactions on Emerging Topics in Computing, 2016.

X. Li and B. Carrion Schafer,Temperature-triggered Behavioral IPs HW Trojan Detection Method with FPGAs, FPL, September, 2015.

Resources:

Synthesizable SystemC designs with Hardware Trojan of different trigger and payload mechanisms. Available at: [Resources web page].

High-Level Synthesis Design Space Exploration

Ongoing

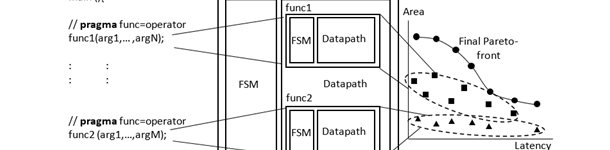

The main objective in design space exploration (DSE) is to find optimal implementations with respect to several, often conflicting, objectives, e.g. area, latency, throughput, power. These optimal implementations are called Pareto-optimal designs. The objective is to find all the designs at the efficient frontier also called Pareto front. The trade-offs can easily be explored within this set rather than considering the entire design space, which would be impractical and irrelevant to the designer. The main problem in DSE is its exponential nature. A brute force approach would eventually find all the Pareto-optimal solutions for smaller designs at a cost of extremely high running time. Heuristics need to be developed to reduce runtime and find the best possible solution. These designs found by the heuristics are called non-dominated designs as they dominate the exploration result obtained so far, but not the overall exploration space.

You can find a survey paper that we recently published describing different approaches here:

B. Carrion Schafer and Zi Wang, High-Level Synthesis Design Space Exploration: Past, Present and Future, IEEE Transactions of Computer Aided Design (TCAD), pp.2628-2639, Vol.39, Issue 10, October, 2020

Key References:

Md Imtiaz Rashid and B. Carrion Schafer, Fast and Inexpensive High-Level Synthesis Design Space Exploration : Machine Learning to the Rescue, IEEE Transactions of Computer Aided Design (TCAD), pp.1-12, 2023.

Z. Wang and B. Carrion Schafer, Partial Encryption of Behavioral IPs to Selectively Control the Design Space in High-Level Synthesis, Design, Automation, and Test in Europe (DATE), pp.1-4, 2019.

B. Carrion Schafer, Parallel High-Level Synthesis Design Space Exploration for Behavioral IPs of Exact Latencies, ACM Trans. Design Autom. Electr. Syst. (TODAES), 2017.

B. Carrion Schafer,Probabilistic Multi-knob High-Level Synthesis Design Space Exploration Acceleration, IEEE Transactions of Computer Aided Design (TCAD), Vol. 35, No.3, pp. 394-406, March 2016.

B. Carrion Schafer and K. Wakabayashi,Machine Learning High Level Synthesis Design Space Exploration, IET Computers & Digital Techniques 6(3), pp. 153-159, 2012.

B. Carrion Schafer and K. Wakabayashi, Divide and conquer high-level synthesis design space exploration, ACM Trans. Design Autom. Electr. Syst. 17(3): 29, 2012.

B. Carrion Schafer and K. Wakabayashi, Design Space Exploration Acceleration through Operation Clustering, IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems (TCAD), Volume 29, Issue 1, pp153-157, Jan. 2010.

Resources:

The following YouTube video shows an example of a HLS DSE explorer built in the lab using a Qt based GUI [Video].